Набор микросхем Intel E7500 представляет

Набор микросхем Intel E7500 представляет следующий шаг в развитии технологии наборов микросхем Intel для серверов. Первый в своем семействе набор микросхем Intel E7500 поддерживает двухпроцессорные серверные платформы, оптимизированные для процессоров Intel Xeon микроархитектуры Intel NetBurst.

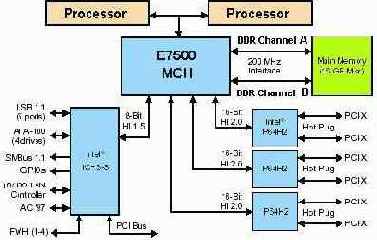

Рис. 4. Структура сервера, созданного на основе чипсета Intel E7500

Чипсет Intel E7500 ориентирован на архитектуру серверов в одно- или двухпроцессорных конфигурациях. Поддерживает системы с процессорами Intel Xeon. Данные процессоры работают с шиной FSB типа QPB (Quad-Pumped Bus), тактовая частота которой для данного чипсета составляет 100 МГц, что обеспечивает скорость передачи данных с частотой 400 МГц (4х - данных и 2х - адреса). Пропускная способность шины процессора - до 3,2 Гбайт/с). Чипсет поддерживает адресацию 36 бит, Symmetric Multiprocessing Protocol (SMP) для двух процессоров, контроль по четности (Parity protection) и т. п.

Чипсет Intel E7500 состоит из трех компонентов - контроллер-концентратор памяти набора микросхем (Memory Controller Hub - MCH), контроллер-концентратор ввода/вывода (I/O Controller Hub 3-S - ICH3-S), контроллер-концентратор 64-разрядной шины PCI/PCI-X (PCI/PCI-X 64-bit Hub 2 - P64H2).

Компонент MCH представлен микросхемой Intel E7500 MCH, содержащей средства интерфейсов работы с процессором, модулями оперативной памяти, а также с микросхемами I/O Controller Hub и PCI/PCI-X 64-bit Hub 2 Встроенный в микросхему Intel E7500 MCH контроллер памяти предусматривает поддержку: двухканального режима работы памяти DDR SDRAM (Double Data Rate SDRAM - SDRAM с передачей данных по передним и задним фронтам тактовых импульсов шины памяти), DDR200, максимального объема памяти - до 16 Гбайт, микросхем 64, 128, 256, 512 Мбит DDR SDRAM, шины памяти 144 бит, модулей регистровой памяти ECC DDR.

Связь с компонентами I/O Controller Hub 3-S и PCI/PCI-X 64-bit Hub 2 осуществляется с помощью хабовых интервейсов (hub interface) - обозначаемые, как HI 1.5 и HI 2.0, соответственно. При этом HI 1.5 - 8 бит, 66 МГц 4x hub interface (256 Мбайт/с), HI 2.0 - 16 бит, 66 МГц 4x hub interface (1 Гбайт/c).

Компонент Р64Н2 представлен микросхемой Intel 82870P2. Он соединяется с контроллером-концентратором MCH через поточечное соединение интерфейса Hub Interface 2.0. К MCH можно подключить до трех устройств P64H2, обеспечивая каждое пропускной способностью свыше 1 Гбайт/с, так что пропускная способность всех устройств ввода/вывода в сумме составит 3,2 Гбайт/с. Каждое устройство P64H2 содержит два независимых 64-разрядных интерфейса PCI-X и два контроллера PCI (по одному на каждый интерфейс PCI-X). Каждый 64-разрядный сегмент PCI-X поддерживает несколько разъемов PCI-X, обеспечивая весьма пропускное соединение для высокоскоростных компонентов, например, таких, как адаптеры Intel Gigabit Ethernet и процессоры ввода/вывода Intel.

Управление традиционными периферийными устройствами осуществляет микросхема ICH3-S, представленная микросхемой Intel 82801CA. Соединяется с контроллером-концентратором MCH через поточечное соединение интерфейса Hub Interface 1.5. Контроллер-концентратор ICH3-S поддерживает устаревшие интерфейсы ввода/вывода, благодаря встроенным специализированным средствам, включая контроллер двухканального устройства Ultra ATA/100 bus master IDE и три контроллера USB для поддержки до шести портов USB. В состав ICH3-S также входит встроенный контроллер SMBus 2.0, встроенный контроллер локальной сети, а также интерфейсы спецификаций AC'97 2.2 и PCI 2.2.

Одновременно с выпуском процессоров Intel Xeon, созданных на основе ядра Prestonia, был анонсирован соответствующий набор системной логики. Этот чипсет, ранее известный как Plumas, предназначен поддерживать данные процессоры и представляет собой развитие чипсета Intel E7500. Новый чипсет получил наименование Intel E7501.

Чипсет Intel E7501 фактически представляет собой усовершенствованный вариант Intel E7500. Отличие Intel E7501 от своего предшественника заключается в поддерживаемых частотах процессорной шины и модулях оперативной памяти.

Если чипсет Intel E7500 обеспечивает поддержку тактовой частоты процессорной шины 100 МГц (частота передачи данных - 400 МГц, адреса - 200 МГц) и модулей DDR200, то Intel E7501 - поддержку тактовых частот 100, 133 МГц (частот передачи данных - 400 и 533 МГц, адреса - 200 и 266 МГц) и модулей памяти DDR200 и DDR266.

Все остальные параметры Intel E7501 совпадают с аналогичными параметрами прототипа - Intel E7500.

Как и его предшественник, чипсет Intel E7501 состоит из трех компонентов - контроллер-концентратор памяти набора микросхем (Memory Controller Hub - MCH), контроллер-концентратор ввода/вывода (I/O Controller Hub 3-S - ICH3-S), контроллер-концентратор 64-разрядной шины PCI/PCI-X (PCI/PCI-X 64-bit Hub 2 - P64H2). При этом компонент MCH, представлен микросхемой Intel E7501, ICH3-S - микросхемой Intel 82801CA, а Р64Н2 - микросхемой Intel 82870P2, то есть последние два из указанного набора компонентов - совпадают с теми же, что и в случае чипсета Intel E7500. Еще одним набором, относящимся к семейству Intel E75xx, является чипсет Intel E7505, известным под кодовым наименованием Placer.

Вообще говоря, этот чипсет не является серверным, а позиционируется как основа для мощных рабочих станций, как, например, Intel 875P. Однако на основе Intel E7505 производители выпускают изделия, представленные в качестве серверных решений.

К слову сказать, если на сайте www.intel.ru чипсет Intel E7505 отнесен к группе наборов для рабочих станций, то на сайте www.intel.ru этот же чипсет представлен как серверный.

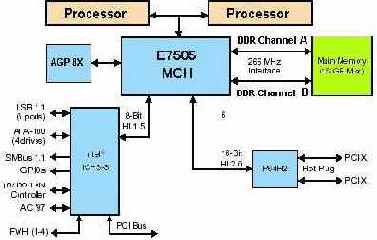

Чипсет Intel E7505 ориентирован для систем одно или двухпроцессорных конфигураций. Поддерживает до двух процессоров Intel Xeon (ядро Prestonia), процессорную шину с тактовыми частотами 133 и 100 МГц (частоты передачи данных - 533 и 400 МГц) и двухканальную конфигурацию оперативной памяти DDR266 или DDR200.

Рис. 5. Структура сервера, созданного на основе чипсета Intel E7505

В отличие от серверных наборов системной логики Intel E7500 и Intel E7501, вместо микросхемы ICH3-S, отвечающей за ввод/вывод, в составе чипсета Intel E7505 используется традиционный компонент ICH4. Кроме того, в архитектуре компонента MCH используется порт AGP 8Х, а в вместо трех микросхем P64H2 в составе чипсета используется одна микросхема данного типа.

Рассмотренные наборы семейства Intel E75xx предназначены для процессоров Intel Xeon архитектуры NetBurst, однако топовыми моделями серверных процессоров этой фирмы являются высокопроизводительные 64-разрядные процессоры Intel Itanium и Intel Itanium 2.

Чипсеты для Intel Itanium / Itanium 2

Для поддержки 64- разрядных процессоров Intel Itanium был разработан набор системной логики Intel 460GX. Этот чипсет является первым набором микросхем, осуществляющий поддержку 64-разрядной микроархитектуры семейства процессоров Intel Itanium. Данный многоконфигурационный набор микросхем оптимизирован для 1-, 2-, 3- и 4-процессорных серверов на базе процессоров Itanium и двухпроцессорных рабочих станций.

Набор микросхем Intel 460GX поддерживает интерфейс контроллера памяти и соответствующие мосты шин PCI, AGP 4X и других стандартных шин устройств ввода/вывода.

Контроллер концентратор памяти представлен микросхемой 82461GX или 82462GX. Осуществляет поддержку памяти PC100 SDRAM объемом до 64 Гбайт, AGP 4X/2X.

Контроллер ввода/вывода - IFB осуществляет поддержку PCI 2.2, ATA33, 2 порта USB, AC'97 и т. п.

Предусмотрено расширение подсистемы ввода/вывода: Мост PCI eXpander (PXB), высокоскоростной мост PCI eXpander (WXB).

Как известно, развитие архитектуры Intel Itanium нашло свое продолжение в линейке процессоров Intel Itanium 2. Для поддержки новых процессоров был разработан специальный набор системной логики, получивший наименование Intel E8870.

Набор микросхем Intel E8870 является первым в архитектуре нового поколения набором микросхем, специально разработанным для удовлетворения требований двух- и четырехпроцессорных серверных платформ высшего уровня. Набор микросхем Intel E8870, оптимизированный для процессора Intel Itanium 2, обеспечивает высокий уровень производительности и масштабируемости, а также предотвращения, обнаружения и исправления ошибок.

Рис. 6. Структура сервера, созданного на основе чипсета Intel 8870

К основным характеристикам чипсета Intel 8870 относятся:

400 МГц, 128-разрядная системная шина, что обеспечивает высокую скорость передачи данных - до 6,4 Гбайт/с,

Очень большой объем оперативной памяти - концентратор DMH предоставляет в сумме 32 разъема для установки памяти на каждый процессорный узел, максимальный объем - 128 Гбайт (с 4 DDR Memory Hubs),

Два высокопропускных масштабируемых порта,

Четыре соединения интерфейса Hub Interface 2.0 с пропускной способностью 1 Гбайт/с на каждое соединение, что позволяет использовать до четырех 64-разрядных контроллера PCI/PCI-X (P64H2) с интерфейсом HI 2.0,

Механизм предзагрузки данных и встроенная кэш-память системы ввода/вывода,

Поддержка высокопроизводительного моста PCI/PCI-X - поддержка всех устройств ввода/вывода PCI/PCI-X I/O, начиная от устаревших PCI и заканчивая высокопроизводительными PCI-X на частоте 133 МГц (каждый контроллер P64H2 содержит два независимых 64-разрядных канала PCI-X с максимальной частотой 133 МГц).

Кроме того, комбинация таких характеристик, как модули "hot-plug" для процессора и памяти, обнаружение и коррекция ошибок, восстановление сбоев устройств памяти (MDFR), резервные пути ввода/вывода и ведение журнала записи ошибок, предоставляет более надежную платформу, уменьшает время простоев для ремонта и обеспечивает целостность передачи данных по всем соединениям и шинам.

Набор микросхем Intel E8870 состоит из следующих компонентов: Intel E8870IO (SIOH), Intel E8870 (SNC), Intel E8870DH (DMH), Intel 82870P2 PCI/PCI-X (P64H2), Intel 82801DB (ICH4). Использование Intel E8870SP - E8870SP Scalability Port Switch (SPS), позволяет расширить возможности чипсета Intel E8870 и создавать системы с восьмью процессорами Intel Itanium.

Рис. 7. Структура сервера c 8 процессорами Intel Itanium, созданного на основе чипсета Intel 8870

В заключение данного краткого обзора следует напомнить, что процессоры новых архитектур, разрабатываемые специалистами фирмы Intel, потребуют новых чипсетов. Поэтому уже в ближайшем будущем нас ожидают новые еще более производительные и функционально насыщенные наборы системной логики, предназначенные для серверных систем.

В статье использованы материалы фирмы Intel